EPSON Oscillator的PLL電路高頻段輸出實現(xiàn)方法

一直以來日本EPSON晶體公司,都是我國甚至全亞洲主要的頻率元件合作商,50%以上的用戶都是選擇使用EPSON Oscillator或者晶體,因為EPSON曾在2010年獲得全球晶體制造商排行第一名.其制造晶體振蕩器的技術(shù),也已達到領(lǐng)先的地步,近年來,EPSON公司一直在攻克PLL電路高頻輸出的實現(xiàn)方法,目前已成功應用到生產(chǎn)制造中,高端產(chǎn)品的”新陳代謝”促進電子元件行業(yè)不斷的突破發(fā)展.

由于電影和其他內(nèi)容傳送服務的普及,數(shù)據(jù)傳輸速度和數(shù)量不斷增加,以支持流經(jīng)互聯(lián)網(wǎng)骨干網(wǎng)的流量不斷增長.對高速通信基礎設施的需求推動了對提供穩(wěn)定輸出信號的高頻參考信號源的強烈需求.一般來說,對于在高頻下振蕩的MHz切割晶體單元,晶體芯片的厚度必須減小(因為厚度決定了AT切割晶體單元振蕩的頻率)但是有限制關(guān)于加工方法,機械強度和易振性.雖然它取決于加工精度,但60MHz是對AT切割晶體的基頻的限制.因此,愛普生定位超過60MHz作為高頻范圍.產(chǎn)生這種穩(wěn)定的高頻參考信號并不是那么簡單,但愛普生有四種方法(技術(shù))來實現(xiàn)高頻振蕩.

在第一種方法中,產(chǎn)生大約20MHz的相對可管理的振蕩頻率的AT切割晶體單元與倍頻器電路或鎖相環(huán)(PLL)電路組合以產(chǎn)生穩(wěn)定的高頻參考信號.產(chǎn)生高頻,穩(wěn)定參考信號的第二種方法是使用表面聲波(SAW)諧振器,它以高頻基頻直接振蕩.第三種方法是使用倒置-mesa型AT切割石英晶體單元,其中僅使用Epson的QMEMS工藝技術(shù)減薄晶體的振動部分.第四種方法是使用以AT切割晶體單元的高階振動的振動模式(泛音).這些技術(shù)說明提供了第一種方法的概要說明,使用倍頻器電路的方法(這里,乘法器電路是指提取諧波分量的模擬乘法器)和PLL電路.

1.倍頻電路提供n度的高頻輸出

倍頻器電路是將特定頻率的電信號轉(zhuǎn)換為增加到第n度的高頻的電路.利用來自典型振蕩電路的輸出信號,形成一定水平的Tr,Tf,Voh和Vol產(chǎn)生包含諧波分量的波形.倍頻器電路有意地產(chǎn)生強調(diào)來自這些諧波的第n個分量的信號,之后使用濾波器來提取第n個分量.使用諧波分量可實現(xiàn)比PLL更低抖動的輸出頻率.但是,當使用僅提取n次諧波的濾波器時,必須使用窄帶寬/帶通濾波器(BPF)來抑制低(n/2和更低)信號分量(子諧波)并限制抖動.此外,在選擇晶體單元時和設計振蕩電路時必須小心,以便源信號不會在n次諧波附近產(chǎn)生雜散信號.因此,用于獲得高頻的產(chǎn)品中使用的技術(shù)通常涉及PLL電路.

2.PLL電路

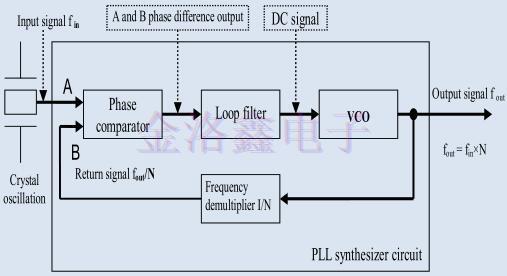

以下是PLL電路的說明,PLL電路是產(chǎn)生穩(wěn)定的高頻信號的另一種基本技術(shù).隨著包括無線通信組件的設備的傳播,用于無線通信的半導體技術(shù)已經(jīng)取得了顯著進步.在這些技術(shù)中,PLL電路技術(shù)的創(chuàng)新尤其令人震驚.PLL電路產(chǎn)生與輸入?yún)⒖夹盘柾降妮敵鲂盘?/span>.利用包括相位比較器,環(huán)路濾波器和壓控振蕩器(VCO)的基本結(jié)構(gòu),PLL電路能夠產(chǎn)生與輸入信號精確同步的信號.與倍頻器電路不同,源信號不用于輸出.PLL電路使用VCO以與源信號不同的頻率產(chǎn)生同步信號.

通過在PLL電路VCO輸出和相位比較器輸入之間插入分頻器,使輸入信號和分頻信號同步,將VCO輸出控制為通過將輸入頻率乘以分頻比而獲得的頻率.為了使該VCO輸出達到與石英晶體振蕩器相當?shù)木?/span>,有必要在使用可產(chǎn)生穩(wěn)定輸入信號的晶體振蕩器或類似元件的同時改變分頻比.這是頻率合成器背后的原理.應用這一原理,AT切割晶體單元的MHz頻帶輸出被輸入到PLL電路,以產(chǎn)生生成GHz頻帶載波的信號,用于無線通信.

圖1.PLL合成器電路基本結(jié)構(gòu)

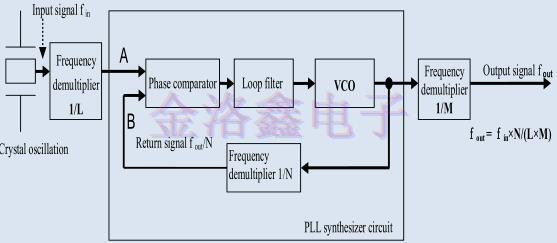

圖2.將頻率分頻器插入輸入的示例

使用PLL電路產(chǎn)生比輸入頻率高許多倍的高頻的關(guān)鍵在于如何使用分頻器.用于實現(xiàn)輸入頻率的n次輸出的方法是圖1中所示的電路配置.另外,如圖2所示,在PLL電路I/O之前和之后插入分頻電路允許精確調(diào)節(jié)輸出頻率.用于增加PLL電路中的頻率設定分辨率的典型方法包括在晶體振蕩源之后直接引入分頻器.然而,使用較高的分頻來增加頻率設置分辨率會導致較低的相位比較頻率,這導致PLL響應性和環(huán)路增益的下降.這反過來又對輸出波形抖動和相位噪聲特性產(chǎn)生負面影響.解決該問題的方法是使用例如分數(shù)PLL.

3.整數(shù)PLL和分數(shù)PLL的特性

PLL晶振電路主要分為兩種類型:整數(shù)和分數(shù).兩種類型都使用振蕩源輸出高頻信號.下面是對主要特性的解釋.顧名思義,整數(shù)PLL能夠產(chǎn)生輸入頻率的整數(shù)倍的輸出頻率.例如,如果要從1MHz源輸出100MHz信號,則分頻器計數(shù)器設置為100.相反,分數(shù)PLL能夠產(chǎn)生輸入頻率的分數(shù)倍的輸出頻率.該電路的優(yōu)點在于它允許您選擇任何頻率(使您能夠獲得精確的頻率設置分辨率).分數(shù)PLL允許精確的頻率分辨率設置,初始頻率偏差可以通過這些屬性精確控制.

然而,缺點是電路設計復雜并且與整數(shù)PLL相比IC的尺寸變大,這意味著傾向于發(fā)生特定的寄生.結(jié)果,通常認為分數(shù)PLL比整數(shù)PLL產(chǎn)生更多的相位噪聲.然而,隨著最近的技術(shù)進步,正在努力減少寄生的發(fā)生,迄今為止這一直是使用分數(shù)PLL的弱點.

愛普生產(chǎn)品陣容和產(chǎn)品功能

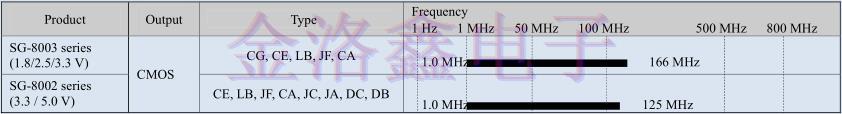

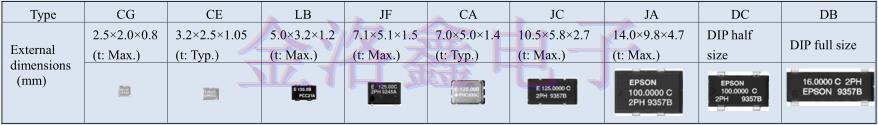

上面,我們研究了使用PLL電路作為實現(xiàn)高頻輸出的方法.這些方法的最大特點是能夠隨意創(chuàng)建所需頻率.換句話說,這些方法可在您需要時提供必要的頻率,包括高頻.愛普生晶振的SG-8000系列采用上面介紹的整數(shù)PLL電路技術(shù),提供各種形狀和尺寸的多樣化產(chǎn)品陣容(表1).我們還提供ROM編寫器(SG-WriterII)作為編程工具,允許客戶將頻率命令寫入SG-8000系列(表2).

SG-8000系列采用AT切割晶體單元.AT切割晶體單元的立方曲線溫度特性保持了給定的溫度穩(wěn)定性,使我們能夠提供具有平滑頻率特性(無頻率跳變)的產(chǎn)品,這些產(chǎn)品不需要在很寬的范圍內(nèi)進行基于溫度的補償.(具有顯著溫度特性的一階線性度的石英振蕩器,例如Si-MEMS振蕩器,需要電路補償以維持給定溫度下的穩(wěn)定性,并且可能導致頻率跳變的發(fā)生.)

EPSON Crystal期待幫助客戶體驗這些晶體單元的高精度特性,以及通過PLL電路技術(shù)實現(xiàn)的自由頻率設置的便利性.最后,下面提供了關(guān)于"倍增"和"PLL"作為用于實現(xiàn)高頻輸出的方法的一些注意事項.乘法:注意電路中產(chǎn)生的次諧波分量,以及低于n/2的分量引起的抖動.PLL:注意環(huán)路帶寬,并在連接到后續(xù)PLL時注意抖動放大和跟蹤.

表1:可編程晶體振蕩器產(chǎn)品陣容

表2:SG-8000系列編程工具

|

|

SG寫入器 |

|

連接器端子 |

usb2.0(最小b) |

|

兼容的操作系統(tǒng) |

Windows7(32位,64位) WindowsVista(32位) WindowsXP(32位) |

|

插座 |

GS-8002,SG-8003 兩個套接字都是可寫的 |

|

軟件 |

SG-WriterII軟件 |

“推薦閱讀”

【責任編輯】:金洛鑫版權(quán)所有:http://www.sxncwy.com轉(zhuǎn)載請注明出處

相關(guān)技術(shù)支持

- MicrochipPCIe技術(shù)開啟多終端連接新時代

- Rakon全新GNSS接收器開啟新太空應用的精準定位時代

- SiTime交響樂系列移動時鐘發(fā)生器助力實現(xiàn)先進的無線連接功能

- 瑞薩半導體為智能建筑注入安全芯動力

- Skyworks新時鐘芯片及發(fā)電機產(chǎn)品解鎖18飛秒抖動特性的黑科技

- Wi-Fi感知松圖電子開啟智能環(huán)境新未來

- SPE網(wǎng)絡設計的革新力量

- CTS西迪斯晶振為預防性維護電流檢測技術(shù)注入精準芯動力

- ECS時序解決方案如何為5G網(wǎng)絡帶來好處

- NX1612SA光刻技術(shù)賦能領(lǐng)航下一代車載通信

手機版

手機版