怎樣可以知道CO振蕩器的低帶寬PLL信號?

在頻率控制元器件行業(yè)中,常用的石英晶體振蕩器類型我們都知道主要有SPXO,VCXO,TCXO,OCXO,VC-TCXO這幾種,很少有人會去了解CO振蕩器(高Q控制振蕩器),它并不屬于常規(guī)的晶振,是為了滿足部分廠家低帶寬PLL的要求.CO受控晶體振蕩器比其他類型的振蕩器穩(wěn)定性要高許多,而且成本比同步時鐘RC振蕩器更低,可以支持更高性能的產(chǎn)品開發(fā)需求.對于低帶寬PLL,高Q控制振蕩器(CO)由于其低增益和高穩(wěn)定性而成為首選器件.本文討論了壓控振蕩器(VCXO),基于變?nèi)荻O管和基于PLL的兩種不同的實現(xiàn)方式.它還討論了數(shù)字控制振蕩器(DCXO),以提高系統(tǒng)設(shè)計的靈活性和穩(wěn)健性,同時考慮量化,更新延遲和環(huán)路濾波器實現(xiàn)對環(huán)路性能的影響.

高穩(wěn)定性受控振蕩器(CO)用于同步或抖動清除PLL,用于網(wǎng)絡(luò),電信,視頻/音頻和儀器儀表應(yīng)用.這種PLL通常具有非常低的帶寬,例如小于1kHz,以從參考輸入時鐘濾除大部分相位噪聲和抖動.這些電路使用高Q機(jī)械諧振器來實現(xiàn)極低的頻率控制增益和高穩(wěn)定性,這是設(shè)計穩(wěn)定的低帶寬PLL所必需的.

兩個主要的高穩(wěn)定性受控振蕩器如下.

1.基于可拉高Q諧振器(VCXO)的壓控晶振

2.基于高Q諧振器的數(shù)字控制振蕩器(DCXO)

當(dāng)PLL的輸入中斷且受控振蕩器有效自由運(yùn)行時,VCXO或DCXO的本機(jī)頻率穩(wěn)定性可以得到改善,以滿足非常嚴(yán)格的穩(wěn)定性要求.示例包括SONET中的同步器和重定時器以及具有保持功能的電信應(yīng)用.在這種情況下,機(jī)械諧振器頻率通過溫度補(bǔ)償技術(shù)(VC-TCXO或DC-TCXO)進(jìn)一步穩(wěn)定,以校正溫度頻率變化或恒溫控制技術(shù)(VC-OCXO或DC-OCXO),以穩(wěn)定諧振器溫度并根據(jù)環(huán)境溫度的變化避免頻率變化.

最廣泛使用的高Q諧振器基于石英晶體或微機(jī)電系統(tǒng)(MEMS)諧振器.這些諧振器分別依賴于石英晶體或硅材料的機(jī)械特性來實現(xiàn)高Q.石英諧振器基于壓電現(xiàn)象操作.當(dāng)在它們的共振頻率下對它們施加機(jī)械應(yīng)力時,這些諧振器產(chǎn)生最大電流.相比之下,目前市售的MEMS諧振器使用靜電激勵來產(chǎn)生高Q振蕩.

高穩(wěn)定性CO使用兩種主要的頻率控制方法,如下所示.

1.直接拉動機(jī)械諧振器頻率

2.使用高分辨率PLL拉

上述頻率控制器件提供不同的功能和優(yōu)點(diǎn),這會影響使用它們的低帶寬PLL的設(shè)計和性能.本文分析了這些特征和優(yōu)點(diǎn),并檢查了由此產(chǎn)生的權(quán)衡.

2.VCXO架構(gòu)和規(guī)范

在解釋不同類型VCXO有源晶振的架構(gòu)和功能之前,讓我們定義如下的關(guān)鍵VCXO規(guī)范.

拉動范圍(PR)

標(biāo)稱條件下全輸入電壓范圍的頻率控制范圍.

絕對拉力范圍(APR)

在整個工作條件范圍內(nèi)保證頻率控制范圍,包括溫度,老化和電壓/負(fù)載變化.由于任何其他因素,APR被計算為PR減去振蕩器頻率穩(wěn)定性.

VCO增益(kv)

給定輸入電壓變化的頻率變化率.該比率表示為Hz/V或ppm/V.

近距離相位噪聲

頻率下的相位噪聲偏移低于10kHz偏移,這通常由輸入電壓噪聲靈敏度決定.

2.1VCXO架構(gòu)

VCXO使用下面列出的兩種頻率控制方法之一.

1.直接拉動機(jī)械諧振器頻率

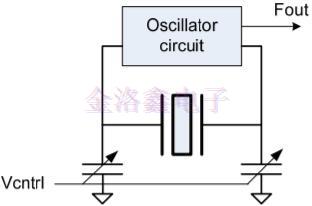

這種類型的VCXO的一個常見例子是基于石英的振蕩器,通過改變分流電容來控制諧振頻率.通常,使用變?nèi)荻O管通過電壓控制電容,從而產(chǎn)生VCXO器件.此示例如圖1所示.

2.使用PLL拉

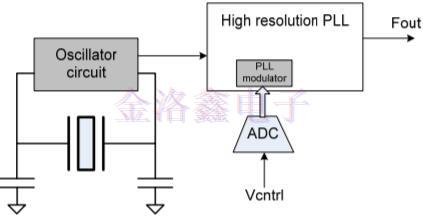

在這種架構(gòu)中,穩(wěn)定的貼片振蕩器輸出驅(qū)動高分辨率PLL,通常是小數(shù)N分頻PLL,以實現(xiàn)足夠高的分辨率.PLL調(diào)制器使用模數(shù)轉(zhuǎn)換器(ADC)以模擬方式驅(qū)動.該架構(gòu)如圖2所示.

圖1:基于拉動諧振器頻率的VCXO

圖2:基于不可拉動諧振器和高分辨率PLL的VCXO

2.2基于變?nèi)荻O管的VCXO

這些VCXO使用變?nèi)荻O管來“拉”石英振蕩器的頻率,并已廣泛用于許多應(yīng)用中.然而,它們的使用需要仔細(xì)權(quán)衡噪聲,APR和Kv.通常,最好為目標(biāo)APR選擇最低Kv,以最小化相位噪聲影響并提高PLL穩(wěn)定性.容納大于+/-100ppm的拉伸范圍可能會對相位噪聲性能或器件的可靠性/質(zhì)量產(chǎn)生不利影響.Kv線性度與控制電壓的關(guān)系在10%范圍內(nèi),這會影響PLL帶寬和整個工作范圍內(nèi)的穩(wěn)定性.

2.3基于PLL的VCXO

基于PLL的壓控晶體振蕩器使用由高穩(wěn)定性振蕩器驅(qū)動的高分辨率PLL,如基于MEMS或石英的振蕩器,如圖2所示.頻率控制功能通過ADC實現(xiàn),數(shù)字化輸入電壓并驅(qū)動小數(shù)N分頻PLL調(diào)制器.該架構(gòu)具有以下優(yōu)點(diǎn).

•可以輕松實現(xiàn)0.1%至1%的Kv線性度

•可以在不影響MEMS或石英振蕩器質(zhì)量的情況下實現(xiàn)寬拉動范圍(>1000pm).但是,這種VCXO確實需要額外的ADC和分?jǐn)?shù)PLL電路.ADC數(shù)字分辨率通常設(shè)計為小于AC電路的熱噪聲.ADC之后是低通濾波器,以最大限度地降低熱噪聲和量化噪聲.由于熱噪聲的抖動效應(yīng),整個電路允許有效的無限分辨率.因此,從應(yīng)用的角度來看,直接模擬控制與使用這種ADC在頻率控制分辨率方面沒有區(qū)別.

ADC噪聲對近端相位噪聲的影響取決于拉動范圍.拉動范圍越大,輸出對輸入噪聲越敏感.對于低拉范圍,在±50ppm或更低的范圍內(nèi),噪聲影響通常是最小的,這意味著近端相位噪聲主要由振蕩器相位噪聲決定.

Vin噪聲影響與拉動范圍成比例增加,每拉動一倍的范圍大約為6dB.基于變?nèi)荻O管的石英VCXO也是如此.因此,在兩種類型的VCXO晶振中都存在近景相位噪聲和拉動范圍之間的折衷.

“推薦閱讀”

相關(guān)常見問題

- 解鎖CTS-CS-BAX-20母線電流傳感的奧秘與應(yīng)用

- bliley晶振CMOS與LVCMOS如何選擇

- bliley射頻PCB設(shè)計避坑指南打造高性能電路板

- 汽車電路安全新護(hù)盾Diodes雙通道高壓側(cè)開關(guān)

- 5G基站的心臟起搏器NDK晶振OCXO

- 使用Suntsu的超低抖動振蕩器來消除信號抖動問題

- Pletronics普銳特新型頻率控制技術(shù)與傳統(tǒng)石英技術(shù)的對比分析

- Golledge頻率控制在可穿戴設(shè)備和健康監(jiān)測中的作用

- 壓電傳感器的工作原理是什么?

- Jauch頻率控制產(chǎn)品高溫環(huán)境下保持冷靜

手機(jī)版

手機(jī)版